# **80386:** A Beginning of 32-bit Microprocessor by Intel

Anas Sayed<sup>1\*</sup>, Shaikh Mohd Ashfaque<sup>2</sup>

<sup>1,2</sup>Department of Computer Engineering, Rizvi College of Engineering, Mumbai, India

\*Corresponding Author: anas11.sayed@gmail.com, Mob: 9619799074

DOI: https://doi.org/10.26438/ijcse/v8i10.8082 | Available online at: www.ijcseonline.org

Received: 09/Oct/2020, Accepted: 19/Oct/2020, Published: 31/Oct/2020

*Abstract*— We do have a general idea about the history of microprocessors. The microprocessor has evolved over the years; from the; 'first single-chip' microprocessor introduced by Intel-the INTEL 4004, that was a 4-bit microprocessor to the recent 64-bit microprocessors. History has it; Intel has been a leader in technology innovation. Intel has given some of the biggest contributions to the evolution of microprocessors. One such salient microprocessor introduced by Intel 80386, which is also known as i386 or 386. 386 was the first 32-bit microprocessor launched in October 1985 that brought along the feature of virtual mode.

*Keywords*—32-bit microprocessors, virtual, 3<sup>rd</sup> gen, intel, x86 family, 386.

## I. INTRODUCTION

The Intel family of microprocessors is quite diverse, but this text specifically concentrates on 80386 that was subsequently renamed as 80386DX to avoid confusion. This was the first 32-bit microprocessor launched by Intel. 80386 is a part of the x-86 family or rather it specifically belongs to the IA-32(Intel architecture, 32-bit), 3rd generation microprocessors. The term "x86" came into being since the names of several successors of Intel's 8086 processor end in "86", including the 80186, 80286, 80386 and 80486 processors. The biggest disadvantage of the 8086 chip is its memory model.

Intel came up with the 8086 to use memory in segments, rather than using one big, flat address space. Although the 80286-chip increased in performance due to non-multiplexed address and data buses as compared to 8086 and multitasking support, the 386 chip's feature of virtual mode was still an asset as it allowed running of 8086 in protected mode. Need for higher clock speed and enhanced memory model brought about the birth of 386.

The 80386 was introduced in October 1985, whereas the manufacturing of microprocessors significantly commenced in June 1986. These processors were fully backward compatible with previous generations of x86 processors and introduced a number of major new features including enhancements to protected mode and 'virtual 8086 mode'. The changes introduced by 386 set a bar for all future 32-bit x86 processors. This text focuses on studying the architecture, organization, and features of 80386, also what changes did a 32-bit architecture brought as compared to the previous generation microprocessors of the x86 family.

## II. RELATED WORK

The 80386 microprocessor is a full 32-bit version of the earlier 8086 / 80286 16-bit microprocessors and represents a major advancement in the architecture a switch from a 16- bit architecture to a 32-bit Architecture [1]. The author further explains the pin diagram and assembly language of the 80386 micro-processor in the paper.

The purpose of this study is to provide a solution for 80386 emulation, it also contains a detailed study on 80386DX that includes its architecture, structure, functioning process, etc. The study shows that a new series of registers was one of the features of 386 as it was not available in any other previous chips of x86 family.

#### III. AN OVERVIEW OF 80386DX

The demand by applications for faster microprocessor speed, more memory, and wider data paths led to the arrival of 80386DX in 1986. The 80386 represented a major overhaul of the 16-bit 8086-a80286 architecture. It was Intel's first practical 32-bit microprocessor that contained a 32-bit data bus and a 32-bit memory address. This is stated in the context that Intel also produced an earlier 32-bit microprocessor called the iapx-432 which turned out to be unsuccessful. Through these 32-bit buses, the 80386DX chip addressed up to 4G bytes of memory. Thus, a 4G-byte memory can store an astounding 1,000,000 typewritten, double-spaced pages of ASCII text data. The 80386 is a sophisticated chip optimized for multitasking in operating systems.

The original concept of the 386 chip was to devise a 32-bit architectural extension to Intel's 8086 and 286 microprocessors that would remain compatible with all the old software, said John Crawford, lead architect on the

#### International Journal of Computer Sciences and Engineering

project. The term 32-bit states that this processor consists of 32-bit registers and data paths supporting 32-bit addresses and data types. With a 32-bit address bus, the 80386 can address up to 4GBytes of physical memory. The physical memory is organized in terms of segments of 4GBytes at most. The 80386 processor supports 16K variety of segments and so the complete virtual area of: 4GBytes \* 16K = 64Terabytes.

Some other on-chip facilities of 386 include address translation registers, advanced multitasking hardware, and paged virtual memory. Special debugging registers provide data and code breakpoints that also work in ROM-based software.

The 80386 was available in a few modified versions such as the 80386SX, which addressed 16M bytes of memory through a 16-bit data and 24-bit address bus, and the 80386SL/80386SLC, which addressed 32M bytes of memory through a 16-bit data and 25-bit address bus. The 80386SLC version of 386 contained an internal cache memory allowing it to process data at even higher rates.

The 80386EX chip is known as an embedded PC as it contains all the parts of the AT category PC on a single integrated circuit. The 80386EX additionally contains twenty-four lines for input/output information, a 26-bit address bus, a 16-bit data bus, a DRAM refresh controller, and programmable chip select logic.

Besides providing higher clock speed, the 80386 included a memory management unit that allowed memory resources to be allocated and managed by the operating system. In earlier microprocessors, memory management was completely dependent on the software. With 80386 we got a hardware circuitry for memory management and memory assignment, making it efficient and reducing software overhead. The instruction set of 80386DX was upward-compatible with the earlier versions of the x86 family. Also in addition to this, there were some instructions referencing the 32-bit registers that managed the memory system. As well as the memory management instructions and techniques used by the 80286 were also compatible with the 80386 micro-processor. As a result of these features being included in the 386, older, 16-bit software could operate on the 80386 micro-processor.

The various versions of 80386 are:(a)80386DX (b)80386SX (c)80386EX

The 80386SX is a reduced bus version of 386 whereas the 80386EX is known as the embedded pc that incorporates the AT bus system, DRAM controller, programmable chip selection logic.

Each 80386 output pin was capable of providing 4.0 mA for address and data connection and 5.0 mA for other connections. This results in an increase in drive current as compared to 2.0 mA provided in earlier microprocessor output pins.

The memory in 80386 is organized in four banks so that it can be accessed as 8, 16, 32 bit as required. The 386 included a series of special-purpose registers that were not found in the earlier microprocessors by Intel. These registers included control, test and debug registers. Control registers are identical to the MSW that was available in the 80286, except that it had an increased bit size.

The features provided by debug register were an expanded version of the basic trapping or tracing allowed in earlier microprocessors. The test registers are used to test the translation look-aside buffer. The memory management unit of 386 included paging unit that was not found in 80286. This feature allowed any software that was written to virtually operate on any memory location. According to studies earlier Intel microprocessors had no such flexibility.

### IV. DESIGN AND ANALYSIS

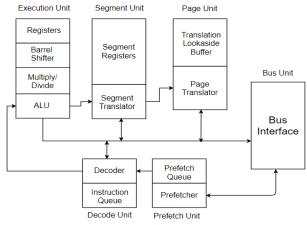

Fig 3.1 Functional block diagram of 80386

The internal design of 80386 is split into three sections:

- 1. Central Processing Unit.

- 2. Memory Management Unit.

- 3. Bus Interface Unit.

In addition to this, the central processing unit is then divided into:

Execution Unit and Instruction Unit.

The Execution unit has eight general-purpose registers which are used in physical address generation, to hold 8 or 16 or 32-bit data and a 64- bit barrel shifter used to increase the speed of shift, rotate, multiply and divide operations and eight special registers that are used for handling knowledge or scheming offset addresses.

The Instruction unit decodes the op-code of the instructions which is read from the memory and stores them in the decoded instruction queue for immediate use by the execution unit during execution.

The Memory Management Unit (MMU) has two subunits i.e. Segmentation Unit and Paging Unit.

© 2020, IJCSE All Rights Reserved

Memory is divided into one or more variable-length segments and every 64 Kbytes or 4 Gigabytes in size depending on memory management techniques used either segmentation or paging. On 386, each task can have at most 16,381 segments that are of 4GB each. This provides 64 TB of virtual memory to each task. In segmentation unit 80386 provides four-level protection for protecting user programs and the operating system from each other.

The Bus Unit consists of a prioritizer that resolves the priority of various bus requests. It controls access to the bus.

#### The Virtual 8086 Mode of 80386:

The V86 mode is a dynamic mode in which the processor can switch rapidly between V86 mode and protected mode. This allows the running of 8086 software in protected mode. The CPU will enter from protected mode to V86 mode to execute an 8086 program, then re- enters protected mode to execute a native 80386 program. This special mode was designed to execute multiple 8086 realmode software applications at a time. The V86 mode is entered by changing the VM bit in the EFLAG register to logic 1. This is done via an IRET instruction if the privilege level is 00. Thus, this bit cannot be set in any other manner. V86 mode helped in sharing a microprocessor among many users by partitioning the memory so that each user could have its own DOS partition. It is noted that there are some differences to the V86 mode as compared to the actual 8086 mode. This includes the instruction clock count, LOCK being restricted to certain instructions, NMI interrupting NMI handlers.

#### V. CONCLUSION

The previous versions though were remarkable during their time, they did lack as time passed and demands increased. Our study shows that the new 386 brought various features to the generation of microprocessors, in which the most significant one was the 32-bit size that included a 32-bit address and data bus. Along with the 80386 chip the Intel also gave versions of this chip that was the 80386SX and 80386EX. The 80386SX was a more popular and less costly version of 80386. The paging unit was also one of the features introduced in this microprocessor and also the virtual mode that interfaced with the 8086 micro-processor. This satisfied most of the demands of the applications. The memory management unit of 80386 provided four levels of protection and optional on-chip paging. The 80386 was the first 32-bit microprocessor introduced by Intel that did set a standard for later versions of x86 family and it indeed was an astounding contribution to the industry by Intel.

#### REFERENCES

Sameera A'amer Abdul-Kader, "*Emulation of the microprocessor intel 80386*", Diyala Journal of Engineering Sciences, Vol.2, No.1, pp. 13-34, 2009.

- Barry B. Brey, "Intel Microprocessors", Pearson Prentice Hall, Ohio, pp. 677-718, 1987.

- [3] Sen-Cuo Ro, Sheau-Chuen Her, "i386/i486 Advanced Programming", Springer Publishing Co Inc., U.S., pp. 54-196, 1993.

- [4] Tiwari, R. Sam, and S. Shaikh, "Analysis and prediction of churn customers for telecommunication industry," 2017 International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), Palladam, 2017, pp. 218-222. doi: 10.1109/I-SMAC.2017.8058343

- [5] S. Navadia, P. Yadav, J. Thomas and S. Shaikh, "Weather prediction: A novel approach for measuring and analyzing weather data," 2017 International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), Palladam, 2017, pp. 414-417, doi: 10.1109/I-SMAC.2017.8058382

- [6] Vidhi Tiwari, Pratibha Adkar "Implementation of IoT in Home Automation using android application" IsroSet-Journal (IJSRCSE), Vol.7, Issue.2, pp.11-16, Apr-2019

- [7] A. Fasiku, Ayodeji Ireti, B. Olawale, Jimoh Babatunde, C. Abiola Oluwatoyin B., "Comparison of Intel Single-Core and Intel Dual-Core Processor Performance", International Journal of Scientific Research in Computer Science and Engineering, Vol.1, Issue.1, pp.1-9, 2013

- [8] M. Sora, J. Talukdhar, S. Majumder, P.H Talukdhar, U. Sharmah, "Word level detection of Galo and Adi language using acoustical cues", International Journal of Scientific Research in Computer Science and Engineering, Vol.1, Issue.1, pp.10-13, 2013

- [9] Manish Mishra, Piyush Shukla, Rajeev Pandey, "Assessment on different tools used for Simulation of routing for Low power and lossy Networks (RPL)", International Journal of Scientific Research in Network Security and Communication, Vol.7, Issue.4, pp.26-32, 2019

- [10] Neha N. Badwaik, Achal J. Wakade, SudhaShrikanth "Underground Cable Fault Detection System by Using IoT" Journal (IJSRNSC), Vol.8, Issue.1, pp.25-28, Feb-2020

### **AUTHORS PROFILE**

Anas Sayed is pursuing Bachelor of Engineering in Rizvi College of Engineering which is affiliated to Mumbai University.

Sheikh Mohd. Ashfaque is currently working as an Assistant Professor in the department of Computer Engineering at Rizvi College of Engineering.